Reference

http://www.zpss.aei.polsl.pl/content/dydaktyka/SD/Xilinx/lab6.pdf

為了想要看到上篇spi出來的訊號是不是跟我在scope看到的一樣

所以研究了一下怎麼simulate

microblaze

本來是想要用外加chipscope來看波形,但是總出現PR

Error

後來搜尋了一下用simulate

microblaze, 我覺得因為ISE版本改很大

所以我在網路上找到的例子都不適用在ISE

14.4,別人可以check的button我的都是disable

直到找到這篇reference,我的心靈才得到了救贖阿!!!!

原來chipscope本來就可以內嵌進去microblaze,不用另外寫程式!

這麼方便的事情我竟然到今天才發現(崩╰(〒皿〒)╯潰

)

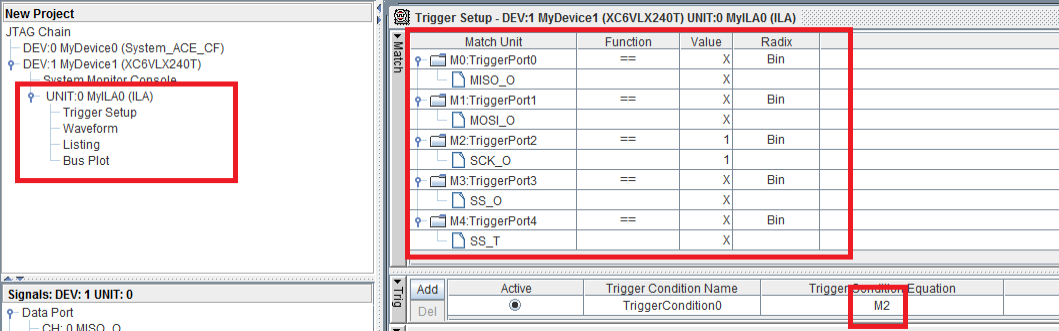

在xps上選擇Debug->Debug

Configuration

然後按左下角的Add

ChipScope Peripheral,就會出現一個讓你選要加IBA,ILA

or VIO

因為我要看得只是spi的master

output 訊號,所以用ILA就可以了

然後會出現選項讓你選你要觀察哪個訊號,我把SPI中要觀察的訊號分別接到不同的triger當中,這樣比較好控制,下面的butter長度可以拉長一點,clk記得要選對,我一開始選200m的osc,後來PR

Error, FSL也不行,可能其他選項的CLK可以,還沒試過

建立完以後,會在Interface看到vio與ila

Hardware->Generate Netlist

然後在ISE重新generate

bit file

在xps上Project->Export

Hardware Design to SDK

確定elf檔compile成功以後programm

FPGA

把bit,bmm,elf檔燒入之後

Run->Run Configuration,在Xilinx

C/C++ ELF下面新增,會自動加入spi_test

Debug

然後run就會Debug進入main的第一行等待,如果之後要從新debug,要按Run->Debug

history->spi_test Debug

然後打開chipscope設定trigger的條件,不用重燒一次bit

file

先觀察右邊是不是有看到ila

然後trigger的數量跟我設定的一樣,改不改名都可以

我把trigger條件設定在sck拉高的時候,因為它是active

high

如果要加入其它的條件可以在下面設定與M2

and 或是or

然後按run等待sdk發出指令來trigger訊號,在sdk上可以resume也可以stepover,看實際需求,然後就可以在chipscope上面看到spi的訊號了

看到圖形後果然ss是active

low,但是匪夷所思的是為甚麼是在tri-state!!!!

然後正常的ss卻沒有啦low,但是我在Scope上看到的是active

high阿!

果然bug沒有解完的一天!

But anyway! Its nice to learn something new !

沒有留言:

張貼留言