Referece : State

Machine Coding Styles for Synthesis - Clifford

E. Cummings

最近心血來潮想要把Clifford

E. Cummings

寫過的文章都看過一次做個整理,正好看到FSM,最近工作上也寫到了兩個FSM,便先讀了OO無雙的FSM詳細介紹,原來我之前寫的FSM是不好的Coding

style阿@@,後來看到altera官方出的VHDL

MOORE&MEALY FSM,果然跟OO推薦的寫法一致,快點來做個練習矯正自己不好的Coding

Style !!!!!!

斯斯有兩種!

一種叫摩爾,一種叫米粒(亂入XDDDD),常用的是Moore,

Moore的輸出只與現在的狀態有關

Mealy的輸出與現在的狀態與輸入有關

兩者的功能相同但是Mealy的輸出會比Moore早一個clk,因為Moore沒辦法根據輸入的訊號及時做出反應

最好的寫法是用兩個Process來寫FSM

常見的state編碼方式有下列幾種,

binary sequence,gray-code,Johnson,one-hot,almost one-hot, one-hot

with zero idle

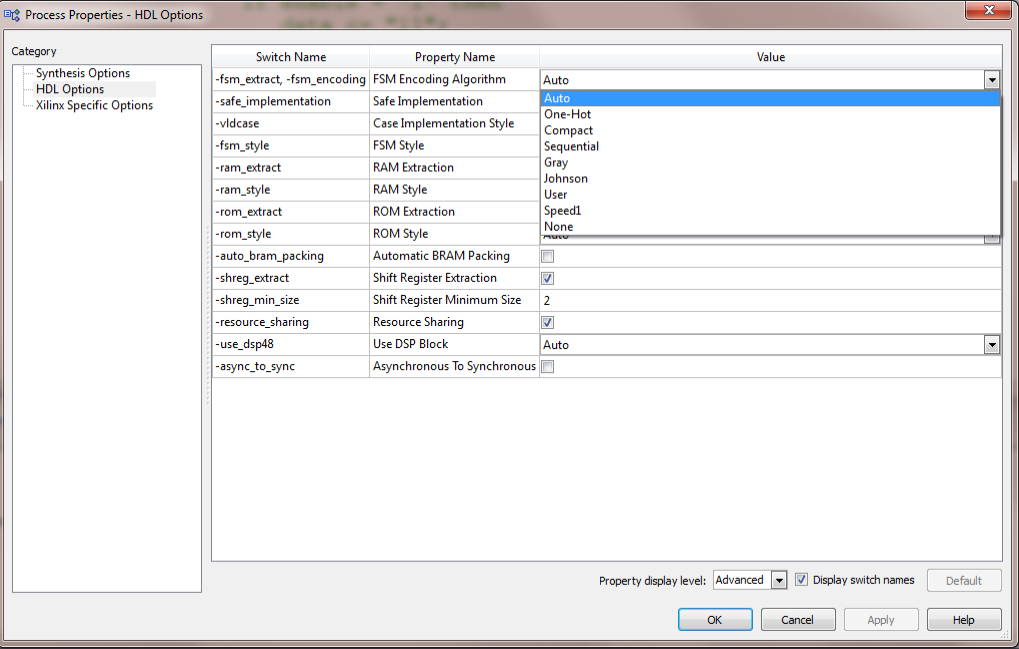

在ise中也可以選要用哪種encode來合成

Moore

FSM

Mealy

FSM

看一下合成Report已經被自動選為gray

code,但也有可能會是binary,系統會自己選擇,因為我設定auto阿!!!

如果要用one

hot也可以透過attribute來改,在程式裡面訊號宣告區加入

attribute syn_encoding : string;

attribute syn_encoding of state :

signal is "onehot";

gray code在狀態轉換的時候可能會使輸出產生突波,而one

hot可以避免這種情形,但是one

hot需要使用比較多的DFF,但是因為每次只變化2個Bit,所以也比較省power

我以前在寫FSM的時候,都把next

state logic與

output

logic放在一起,OO無雙說,這樣會增加程式的複雜度,使維護困難,它說最好在Moore中的output

logic在擋一級register使timing更好,但是我感覺這樣在模擬的時候,輸出與state差一個clk,會增加debug的難度

沒有留言:

張貼留言